SDR and Cognitive Radio on Parallella

by

Gunnar Hillerström, Swedish Defence Research Agency (FOI)

Andreas Olofsson, Adapteva

In a Software Defined Radio, the aim is to implement as much of the analog circuitry (mixers, modulators, filters etc) as possible in the digital domain. Key components in an SDR are Analog-Digital Converters (ADC), Digital-Analog Converters (DAC), and Digital Signal Processing (DSP). One of the advantages with this approach, apart from the flexibility of having the radio type defined by software is that the hardware Size, Weight and Power (SWAP) can be reduced.

Popular implementations of the SDR concept, such as the open source Universal Software Radio Peripheral (USRP), use a combination of microprocessor and FPGA-technology. The FPGA provides the parallel front end processing and precise timing for the ADC and DAC and signal processing chain (modulation, demodulation and filtering, etc). The processor takes care of the complex back-end higher level functionality. The data rates of the ADCs and DACs at the front end peripheral is typically reduced before being communicated to/from the host processor via the USB or Ethernet. The majority of the software in SDR solutions like GNU radio normally resides on a host PC with graphical output. The combination of a USRP and a standard PC allows developers to easily put together effective SDR solutions with a limited budget.

Closely related to SDR is Cognitive Radio (CR). The main motivation for CR research is the growing problem of spectrum congestion. By using real-time spectrum sensing it will be possible to adapt the radio to utilize unused spectrum. To get good CR performance, the feed-back loop latency from spectrum sensing to usage must be reduced to a minimum; especially if there are multiple Cognitive Radios in the same area. Otherwise the risk of both radios trying to use the same ‘unused’ spectrum and failing is high.

The phrase “Software” in SDR is usually understood to include compiled software running on the microprocessor as well as the bit-streams/firmware loaded onto the FPGAs. However, the difference between the “soft” in the FPGA and the “soft” in the microprocessor is substantial. Updates for well written software running on microprocessors tend to have few side effects and can be supported by a very large community of skilled programmers. In contrast, FPGA firmware updates usually changes the architecture and can only be done by a much smaller community of expert hardware designers. It is generally a good idea to build an SDR architecture that minimizes FPGA firmware changes and encourages all necessary updates to be made within the software running on the microprocessor. The more functionality we can transfer into the true software domain, the lower the development cost and the faster the time-to-market becomes.

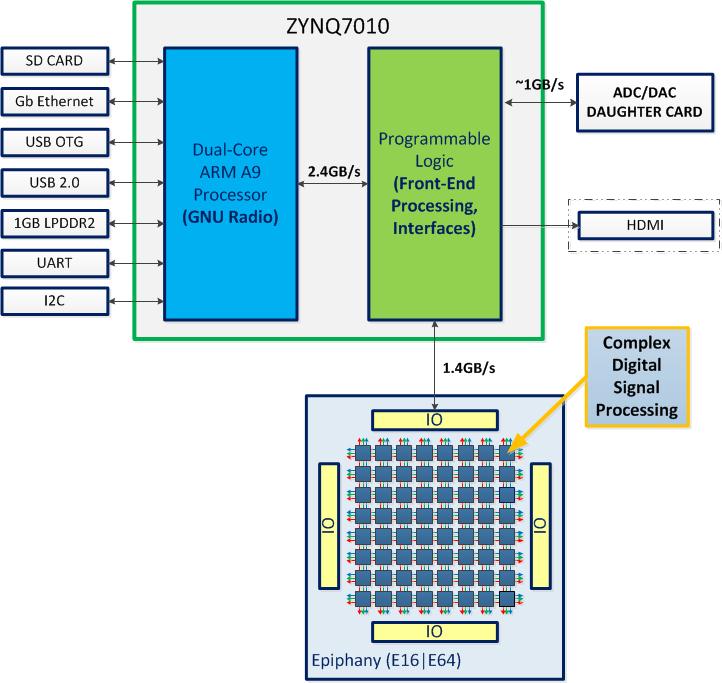

The $99 Parallella board announced by Adapteva recently includes an Epiphany multicore DSP and a Xilinx Zynq-7010 with a dual-core ARM A9 CPU and on chip programmable logic. When combined with a daughter board containing an ADC and DAC, the Parallella board can be used to implement traditional SDR with tight high bandwidth host coupling and any other signal processing wanted. The software that normally runs on the remote host PC can now be run on the tightly coupled Dual-Core ARM A9 host processor in collaboration with the Epiphany multicore DSP. The ample single precision floating point performance offered by the Epiphany should make SDR development significantly easier. Using these Parallella kits the fast closed loop spectrum sensing required for a good Cognitive Radio implementation could also be explored, all within a tight budget and with a foot print of two stacked credit card sized boards.